PCIe 8.0 First Draft Unleashes 1 TB/s Speed and 0.5V Signaling

The PCI-SIG has officially released the first draft of the PCIe 8.0 specification, ushering in a new era of interconnect technology. With groundbreaking bandwidth of 1 TB/s, a lower voltage milestone, and evaluation of fresh connector designs, this standard promises to transform data center, AI, and high-performance computing. Below, we answer the most pressing questions about this upcoming generation.

What exactly is PCIe 8.0 and who announced its first draft?

PCIe 8.0 (also called PCIe Gen 8) is the eighth generation of the Peripheral Component Interconnect Express standard, a high-speed serial computer expansion bus. On [date of original article], the PCI-SIG (the industry consortium that develops the PCIe specification) announced the availability of the first draft version for members. This draft solidifies the core technical targets, including a 256 GT/s (gigatransfers per second) data rate per lane, which aggregates to an enormous 1 TB/s of bidirectional bandwidth in a typical x16 slot configuration. The draft also signals that the group is moving toward final ratification, expected in 2028, giving hardware developers a clear roadmap.

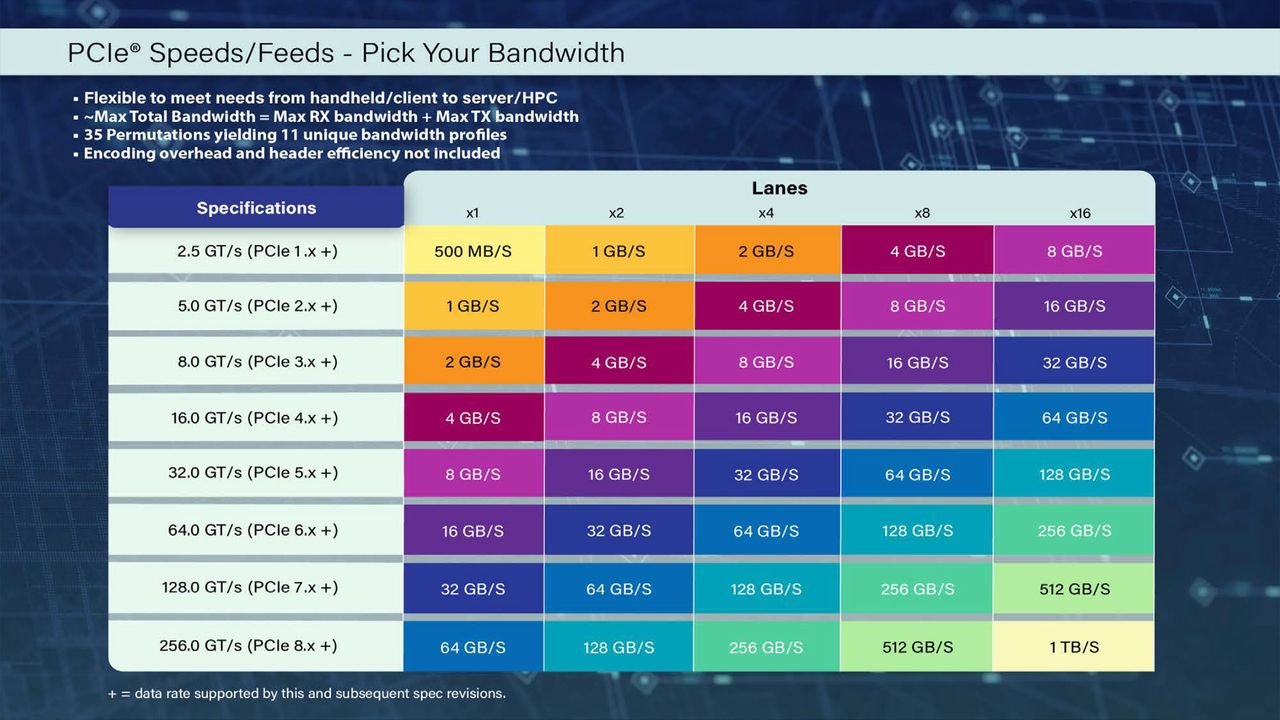

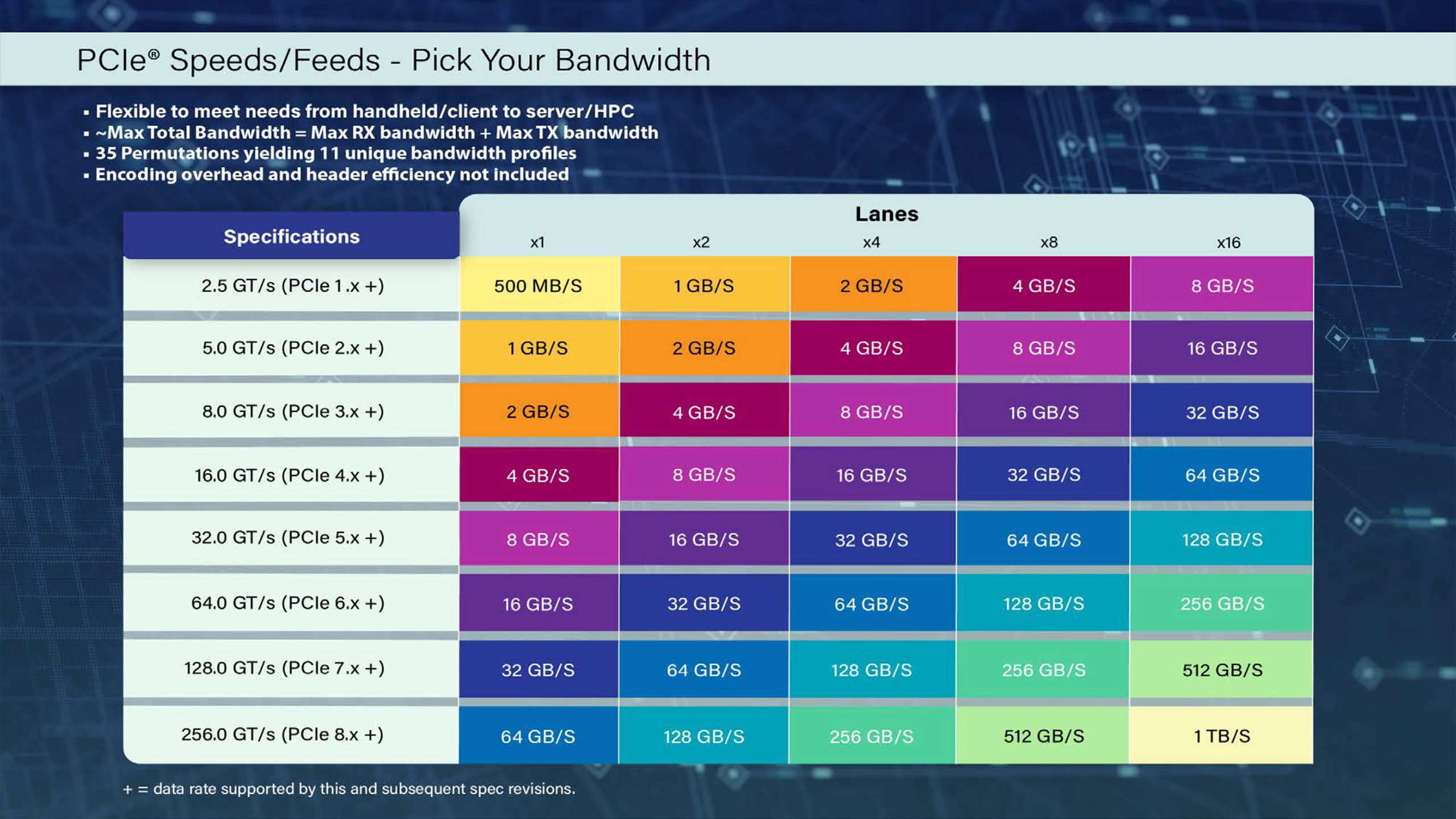

How much bandwidth does PCIe 8.0 actually deliver?

PCIe 8.0 delivers a raw data transfer rate of 256 GT/s per lane. When you consider a standard x16 slot (16 lanes), the total raw bandwidth reaches 1,024 GB/s — or 1 TB/s — in each direction simultaneously, for a combined bidirectional throughput of 2 TB/s. That’s double the bandwidth of PCIe 7.0, which operates at 128 GT/s per lane. To put it in perspective, a single PCIe 8.0 x16 link can transfer the contents of a 4K Blu-ray movie (roughly 100 GB) in under a tenth of a second. This massive data pipe is crucial for emerging workloads like real-time AI inference, high-frequency trading, and next-generation graphics.

What is the 0.5V milestone and why is it important?

One of the key technical achievements in the PCIe 8.0 draft is reaching a 0.5V signaling voltage — down from the 1.8V or lower voltages of earlier generations. This 0.5V milestone marks a major reduction in the voltage swing used to transmit data across PCIe lanes. Lower voltage directly translates into reduced power consumption and less heat generation, both critical for high-density data center servers and mobile devices. Despite the lower voltage, the increased data rate is maintained through advanced equalization and signal integrity techniques. This milestone also helps PCIe 8.0 remain backwards compatible with older hardware without excessive power requirements.

Tell me about the new connector technology being evaluated.

The PCI-SIG is actively evaluating new connector technology for PCIe 8.0 to handle the extreme signal speeds and mechanical demands. While the current draft does not mandate a specific connector, several designs are under consideration including modified edge connectors, M.2-like form factors with higher pin density, and potentially optical interconnects for future revisions. The goal is to maintain electrical and mechanical backwards compatibility with existing PCIe slots while providing better shielding and reduced crosstalk. A new connector would also improve thermal dissipation and support the higher power delivery needed by PCIe 8.0 devices. Final decision on connector specification is expected closer to ratification in 2028.

Does PCIe 8.0 maintain backwards compatibility with older generations?

Yes, the PCI-SIG has reassured that PCIe 8.0 will maintain full backwards compatibility with PCIe 7.0, 6.0, 5.0, 4.0, 3.0, 2.0, and 1.0 devices and slots. This means you can plug a PCIe 4.0 graphics card into a PCIe 8.0 slot (or vice versa), and the system will negotiate the highest common speed. However, to achieve the full 256 GT/s, both the host and device must support PCIe 8.0, have the new low-voltage signaling, and use compatible connectors. Backwards compatibility is achieved through the same auto-negotiation mechanisms used in previous generations, ensuring a smooth transition for existing infrastructure.

When will PCIe 8.0 be finalized and ratified?

According to the PCI-SIG, the final ratification of the PCIe 8.0 specification is expected in 2028. The first draft was released in [current year? actually 2025?]. The timeline typically includes several revision drafts, feedback loops, and interoperability testing before a final version is published. Following ratification, chip vendors and device manufacturers will begin designing compliant products, with the first PCIe 8.0 devices likely appearing in late 2028 or early 2029. It's worth noting that each new generation takes roughly 3-4 years from draft to market availability, so early adopters may see evaluation hardware by 2027.

How does the 256 GT/s data rate compare to earlier PCIe generations?

PCIe 8.0's 256 GT/s per lane represents a doubling over PCIe 7.0's 128 GT/s, which itself doubled PCIe 6.0's 64 GT/s. For reference, PCIe 5.0 offers 32 GT/s per lane, PCIe 4.0 16 GT/s, and PCIe 3.0 8 GT/s. In terms of raw x16 bandwidth: PCIe 3.0 ~16 GB/s, PCIe 4.0 ~32 GB/s, PCIe 5.0 ~64 GB/s, PCIe 6.0 ~128 GB/s, PCIe 7.0 ~256 GB/s, and now PCIe 8.0 ~1,024 GB/s — a full terabyte per second. This dramatic scaling is achieved through advanced modulation schemes (PAM-4 signal encoding) and higher lane rates, while maintaining backward compatibility. It's a testament to PCI-SIG's continued innovation.

What applications will benefit most from PCIe 8.0's performance?

PCIe 8.0's 1 TB/s bandwidth is tailor-made for data-intensive workloads such as: AI and machine learning training clusters that require massive data movement between GPUs and accelerators; high-performance computing (HPC) nodes interconnecting multiple CPUs and FPGAs; data center storage arrays using NVMe over PCIe; real-time video processing (8K/16K streams); network interface cards for 800GbE and beyond; and high-frequency trading systems where every nanosecond counts. Additionally, consumer applications like ultra-high-resolution gaming and virtual reality will eventually leverage PCIe 8.0 for seamless asset streaming. The lower voltage and improved efficiency also make it attractive for power-constrained environments.